# ACM3129B 2×57W Stereo | 1×110W Mono, Analog Input Class-D Audio Amplifier with Ultra Low Power Dissipation, Spread Spectrum and AGL

#### 1. Features

## Single Supply Voltage

- PVDD: 8V to 26.4V

- Built-in LDO output 5V for others

## Various Output Configurations

- 2× 57W, 1% THD+N, 24V, 4Ω, BTL

- 1×110W, 1% THD+N, 24V, 2Ω, PBTL

#### Excellent Audio Performance

- THD+N ≤ 0.02% at 1W, 1kHz, 4Ω, PVDD = 24V

- Higher Order Modulator Enable Better THD+N for full audio band

- Idle switching A-weighted noise  $\leq 63 \ uV_{RMS}$

#### Efficient Class-D Operation

- >90% efficient Class-D operation eliminates need for heat sink

- Low Idle Current: <24mA, PVDD=12V, LC Filter=10uH+0.68uF

- Patented Modulation Schemes to Minimize inductor ripple

Current for all output power level

## Low EMI Technology

- Spread Spectrum Option

- 180° PWM Phase Shift

## Gain Management

- 20dB, 26dB, 30dB, 34dB fixed gain setting

- Mute Operation to stop PWM switching

- Programmable Power Limit

- Automatic Gain Limit /AGL

- Avoid POP caused by unplugging

#### Analog Protections

- Short-Circuit protection with Auto-recovery option

- Under-Voltage detection

- Over-Voltage detection

- Output DC detection for speaker protection

- Over temperature protection with auto recovery

## 2. Applications

- Bluetooth/Wireless Speakers

- Soundbars

- Docks, Monitors

- Home Theaters

- LCD TV/PC

# 3. General Description

The ACM3129B is a stereo/mono, Class D audio amplifier delivers up to  $2\times57W$  into  $4\Omega$  stereo mode and  $1\times110W$  into a  $2\Omega$  load in mono mode while offering up to 92% efficiency. In order to minimize power dissipation, a new patented modulation scheme - Dynamic PWM been used to minimize inductor loss for full output power range.

The ACM3129B operates from a single +4.5V to +26.4V supply, driving the load in BTL or PBTL configuration.

The ACM3129B offers a spread-spectrum modulation mode that reduces EMI noise and provide 2 switching frequency option (384kHz, 480kHz).

Features include fully differential inputs, comprehensive popand click suppression, and four selectable-gain settings (20dB,26dB,30dB and 34dB). A pin adjustable power limit function and speaker DC protection protect speaker without damage. Short-circuit protection, Over-temperature protection and Over/Under Voltage protection prevent the device from being damaged during a fault condition.

## 4. Device Information

| Part number Package |          | Body size       |

|---------------------|----------|-----------------|

| ACM3129B            | TSSOP 28 | 9.7 mm × 4.4 mm |

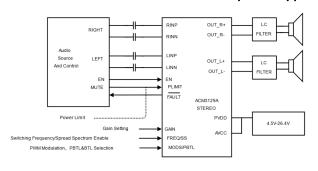

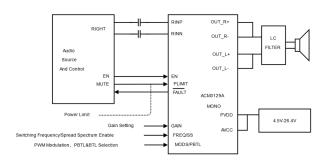

## Simplified Application Circuit

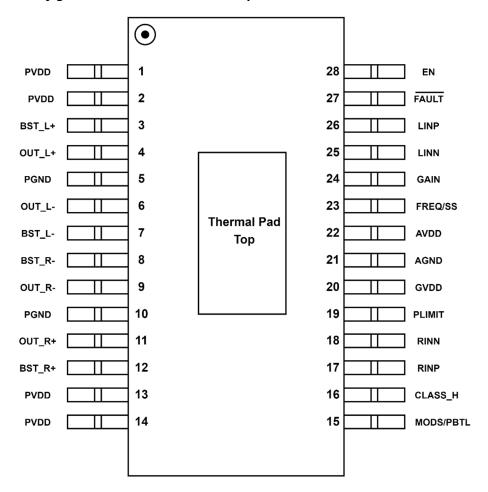

# 5. Pin Configuration and Function Descriptions

| Pin No. | Name      | Туре | Description                                                                                       |  |

|---------|-----------|------|---------------------------------------------------------------------------------------------------|--|

| 1       | PVDD      | PWR  | Power Supply                                                                                      |  |

| 2       | PVDD      | PWR  | Power Supply                                                                                      |  |

| 3       | BST_L+    | BST  | Boot strap for positive left channel output, connect to 470nF X5                                  |  |

|         |           |      | better ceramic cap to OUT_L-                                                                      |  |

| 4       | OUT_L+    | PO   | Positive left channel output                                                                      |  |

| 5       | PGND      | G    | Ground                                                                                            |  |

| 6       | OUT_L-    | PO   | Negative left channel output                                                                      |  |

| 7       | BST_L-    | BST  | Boot strap for negative left channel output, connect to 470nF X                                   |  |

|         |           |      | or better ceramic cap to OUT_L-                                                                   |  |

| 8       | BST_R-    | BST  | Boot strap for negative right channel output, connect to 470nF X5R                                |  |

|         |           |      | or better ceramic cap to OUT_R-                                                                   |  |

| 9       | OUT_R-    | PO   | Negative right channel output                                                                     |  |

| 10      | PGND      | G    | Ground                                                                                            |  |

| 11      | OUT_R+    | PO   | Positive right channel output                                                                     |  |

| 12      | BST_R+    | BST  | Boot strap for positive right channel output, connect to 470nF X5R                                |  |

|         |           |      | or better ceramic cap to OUT_R+                                                                   |  |

| 13      | PVDD      | PWR  | Power Supply                                                                                      |  |

| 14      | PVDD      | PWR  | Power Supply                                                                                      |  |

| 15      | MODS/PBTL | AIN  | PWM Modulation Selection and BTL/PBTL Selection                                                   |  |

| 16      | CLASS_H   | AO   | Class-H control signal                                                                            |  |

| 17      | RINP      | AIN  | Positive audio input for right channel                                                            |  |

| 18      | RINN      | AIN  | Negative audio input for right channel                                                            |  |

| 19      | PLIMIT    | AIN  | Power limit level adjustment. Connect a resistor divider from GVDD                                |  |

|         |           |      | to GND to set power limit. Give V(PLIMIT)<0.5V to Mute amplifier                                  |  |

|         |           |      | (set amplifier to Hi-Z state, power stage stops switching). Give                                  |  |

|         |           |      | 0.6V <v(plimit)<3v give<="" level.="" limit="" power="" set="" td="" the="" to=""></v(plimit)<3v> |  |

|         |           |      | V(PLIMIT)>4.2V to bypass the power limit function.                                                |  |

| 20      | GVDD      | PO   | 5V regulated output, also used as supply for PLIMIT function                                      |  |

| 21 | AGND    | G   | Ground                                                          |  |

|----|---------|-----|-----------------------------------------------------------------|--|

| 22 | AVDD    | PWR | Analog Supply                                                   |  |

| 23 | FREQ/SS | AIN | Switching Frequency Selection and Spread Spectrum               |  |

|    |         |     | Enable/Disable                                                  |  |

| 24 | GAIN    | AIN | Gain Selection via Pull-down resistor                           |  |

| 25 | LINN    | AIN | Negative audio input for left channel                           |  |

| 26 | LINP    | AIN | Positive audio input for left channel                           |  |

| 27 | FAULT   | DO  | Fault reporting including Over-temperature, DC Detection, Over- |  |

|    |         |     | Current Protection, UV/OV. Open Drain                           |  |

|    |         |     | FAULT = High, normal operation                                  |  |

|    |         |     | FAULT = Low, fault condition                                    |  |

| 28 | EN      | AIN | Enable Logic input for amplifier (LOW=Output Hi-Z, HIGH=Output  |  |

|    |         |     | Enabled). TTL logic levels with compliance to AVDD              |  |

# 6. Device Family Comparison

| Device Name | PVDD Range (V) | Thermal Pad |

|-------------|----------------|-------------|

| ACM3108     | 4.5V-14.5V     | Pad Down    |

| ACM3128A    | 4.5V-26.4V     | Pad Down    |

| ACM3129B    | 4.5V-26.4V     | Pad Up      |

# 7. Specifications

# 7.1 Absolute Maximum Ratings

|                  |                                | MIN  | MAX      | UNIT |

|------------------|--------------------------------|------|----------|------|

| PVDD, AVDD       | Supply Voltage                 | -0.3 | 30       | V    |

|                  | LINP, LINN, RINN, RINP         | -0.3 | 6.3      | V    |

| Input Voltage, V | PLIMIT, MODS/PBTL, FREQ/SS     | -0.3 | GVDD+0.3 | V    |

|                  | FAULT, EN                      | -0.3 | PVDD+0.3 | V    |

| T <sub>A</sub>   | Ambient operating temperature  | -40  | 85       | ℃    |

| Tı               | Operating junction temperature | -40  | 160      | ℃    |

| T <sub>stg</sub> | Storage temperature            | -40  | 125      | ℃    |

<sup>(1)</sup> Stressed beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicted under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                 | VALUE         | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------|---------------|------|

| .,                 |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-<br>001-2017 (1) | <u>+</u> 2000 | W    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002-2018 (2) | <u>+</u> 500  | V    |

- (1) JEDEC document JS-001-2017 states that 2000-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JS-002-2018 states that 500-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

| SYMBOL                | PARAMETER                | TEST CONDITION | MIN | NOM | MAX  | UNIT |

|-----------------------|--------------------------|----------------|-----|-----|------|------|

| V <sub>(SUPLLY)</sub> | Power supply inputs      | PVDD, AVDD     | 8   |     | 26.4 | V    |

| V <sub>IH</sub>       | High-level input voltage | EN             | 2   |     |      | .,   |

| VIL                   | Low-level input voltage  | EN             |     |     | 0.8  | V    |

| SYMBOL                | PARAMETER                      | TEST CONDITION                               | MIN | NOM | MAX | UNIT |

|-----------------------|--------------------------------|----------------------------------------------|-----|-----|-----|------|

| VoL                   | Low-level output voltage       | FAULT, R <sub>PULL-UP</sub> =100kΩ, PVDD=12V |     |     | 0.8 | V    |

| I <sub>IH</sub>       | High-level input current       | EN                                           |     |     | 50  | μΑ   |

| IIL                   | Low-level input current        | EN                                           |     |     | 5   | μΑ   |

| R <sub>L</sub> (BTL)  | Additional land land           | (0 to 110 filter 40 th 0 f0 f)               | 3.2 | 4   |     |      |

| R <sub>L</sub> (PBTL) | Minimum load Impedance         | (Output LC filter=10uH+0.68uF)               | 1.6 | 2   |     |      |

| Tı                    | Junction Operating Temperature |                                              | -40 |     | 160 | ℃    |

| T <sub>A</sub>        | Ambient Operating Temperature  |                                              | -40 |     | 85  | ℃    |

# 7.4 Thermal Information

|                 |                                            | ACM3129B, TSSOP 28 PINS |      |

|-----------------|--------------------------------------------|-------------------------|------|

|                 |                                            | JEDEC STANDARD          | UNIT |

|                 |                                            | 4-LAYER PCB             |      |

| $\theta_{JA}$   | Junction-to-ambient thermal resistance     | 14                      | °C/W |

| θ <sub>ЈТ</sub> | Junction-to-case (top) thermal resistance  | 1.2                     | °C/W |

| ψл              | Junction-to-top characterization parameter | 5.7                     | °C/W |

# 7.5 Electrical Characteristics

PVDD=12V, Fin=1kHz, Load= $4\Omega$ , Bootstrap Capacitor= $0.47\mu\text{F}$ , free-are room temperature 25 C, LC filter=10uH+0.68uF, Fsw=384kHz, BD Mode (unless otherwise noted)

| PARAMETER           |                                  | TEST CONDITIONS                                         | MIN | TYP | MAX | UNIT  |

|---------------------|----------------------------------|---------------------------------------------------------|-----|-----|-----|-------|

| DC Electrica        | al Characteristics               |                                                         |     |     |     |       |

| Vos                 | Class-D output offset voltage    | V <sub>I</sub> =0V, BTL Mode                            | -10 |     | 10  | mV    |

| • 05                | (measured differentially)        |                                                         |     |     |     |       |

| $I_{CC}$            | Quiescent supply current         | EN≥2V, LC filter=10µH+0.68µF, 2×                        |     | 24  |     | mA    |

|                     |                                  | BTL, Dynamic PWM Modulation                             |     |     |     |       |

| I <sub>CC(SD)</sub> | Quiescent supply current in      | EN≤0.8V, PVDD=12V                                       |     | 20  |     | μΑ    |

|                     | shutdown mode                    |                                                         |     |     |     |       |

|                     | Drain-source on-state            |                                                         |     | 75  |     | mΩ    |

| R <sub>DS(ON)</sub> | resistance, High side NMOS       | PVDD=12V, I <sub>OUT</sub> = 500mA, T <sub>J</sub> = 25 |     |     |     |       |

| NDS(ON)             | Drain-source on-state            | 1 VDD-12V, 1001 - 30011A, 13 - 23                       |     | 75  |     | mΩ    |

|                     | resistance, Low side NMOS        |                                                         |     |     |     |       |

|                     |                                  | Pull Down Resistor = 47kΩ                               |     | 20  |     | dB    |

| G                   | Gain                             | Pull Down Resistor≥120kΩ or Open                        |     | 26  |     | dB    |

|                     |                                  | Pull Down Resistor≤4.7kΩ or Short                       |     | 30  |     | dB    |

|                     |                                  | Pull Down Resistor = 15kΩ                               |     | 34  |     | dB    |

| ton                 | Turn-on-time                     | EN≥2V                                                   |     | 40  |     | ms    |

| t <sub>OFF</sub>    | Turn-off-time                    | EN≤0.8V                                                 |     | 5.7 |     | μs    |

| GVDD                | Gate drive supply                | I <sub>GVDD</sub> < 200 uA                              |     | 5   |     | V     |

| AC Electrical       | Characteristics, Stereo Output   |                                                         |     |     |     |       |

| PSRR                | Power supply ripple rejection    | 200mV <sub>PP</sub> ripple at 1kHz, Gain=20dB,          |     | -70 |     | dB    |

|                     |                                  | Input AC coupled to GND                                 |     |     |     |       |

|                     |                                  | THD+N = 10%, f = 1kHz, PVDD = 20V                       |     | 48  |     | w     |

|                     | Continuous output power          | THD+N = 1%, f = 1kHz, PVDD = 20V                        |     | 39  |     | w     |

| P <sub>O(SPK)</sub> | (4 $\Omega$ Load)                | THD+N = 10%, f = 1kHz, PVDD = 24V                       |     | 69  |     | w     |

|                     |                                  | THD+N = 1%, f = 1kHz, PVDD = 24V                        |     | 57  |     | w     |

|                     | Output integrated noise,         | Gain = 20dB                                             |     | 63  |     | μVrms |

| $V_n$               | 20Hz to 22kHz, A-weighted filter | Gain = 26dB                                             |     | 75  |     | μVrms |

|                     |                                  | Spread Spectrum Disable                                 |     | 384 |     | kHz   |

|                     | Switching frequency of the       |                                                         |     | 480 |     | kHz   |

| Fsw                 | speaker amplifier                | Spread spectrum Enable                                  | 345 | 384 | 423 | kHz   |

|                     |                                  |                                                         | 432 | 480 | 528 | kHz   |

|                     | 1                                | 1                                                       | 1   | 1   | 1   | 1     |

| PARAMETER                  |                                                  | TEST CONDITIONS                                                                                | MIN | TYP  | MAX | UNIT  |

|----------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| X-talk <sup>(1)</sup>      | Crosstalk                                        | V <sub>o</sub> =2Vrms, Gain=26dB, f=1kHz, based on ACM3129BEVM                                 |     | 90   |     | dB    |

| AC Electrical C            | haracteristics, Mono Output                      |                                                                                                |     |      |     |       |

| PSRR                       | Power supply ripple rejection                    | 200mV <sub>PP</sub> ripple at 1kHz, Gain=20dB,<br>Input AC coupled to GND                      |     | -70  |     | dB    |

| P <sub>O(SPK)</sub>        | Continuous output power $(2\Omega \text{ Load})$ | THD+N = 10%, f = 1kHz, PVDD = 24V<br>THD+N = 1%, f = 1kHz, PVDD = 24V                          |     | 134  |     | w     |

|                            | Output integrated noise,                         | Gain = 20dB                                                                                    |     | 63   |     | μVrms |

| V <sub>n</sub>             | 20Hz to 22kHz, A-weighted filter                 | Gain = 26dB                                                                                    |     | 75   |     | μVrms |

|                            |                                                  | Spread Spectrum Disable                                                                        |     | 384  |     | kHz   |

| Fsw                        | Switching frequency of the                       |                                                                                                |     | 480  |     | kHz   |

| . 500                      | speaker amplifier                                | Spread spectrum Enable                                                                         | 345 | 384  | 423 | kHz   |

| PROTECTION                 |                                                  |                                                                                                | 432 | 480  | 528 | kHz   |

| PROTECTION                 | Over-Current Error Threshold                     | Creation Output Courset (Part I C                                                              | 7.5 | 8    |     | Α     |

| OCE <sub>THRES</sub>       | Over-current Error Threshold                     | Speaker Output Current (Post LC filter), Speaker current, PVDD=15V                             | 7.5 | 0    |     | ^     |

| UVE <sub>THRES(PVDD)</sub> | PVDD under voltage error threshold               | , , , , ,                                                                                      |     | 7.5  |     | V     |

| OVE <sub>THRES(PVDD)</sub> | PVDD over voltage error threshold                |                                                                                                |     | 29.2 |     | V     |

| DCE <sub>THRES</sub>       | Output DC Error protection threshold             | Class D Amplifier's output DC voltage cross speaker load to trigger Output DC Fault protection |     | 2.5  |     | V     |

| T <sub>DCDET</sub>         | Output DC Detect time                            | Class D Amplifier's output remain at or above DCE <sub>THRES</sub>                             |     | 700  |     | ms    |

| OTE <sub>THRES</sub>       | Over temperature error threshold                 |                                                                                                |     | 160  |     | °C    |

| OTE <sub>Hysteresis</sub>  | Over temperature error hysteresis                |                                                                                                |     | 30   |     | ℃     |

Crosstalk high depends on output layout (L channel and R channel routing distance), Inductor type.

# **Typical Characteristics**

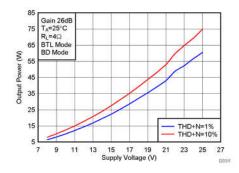

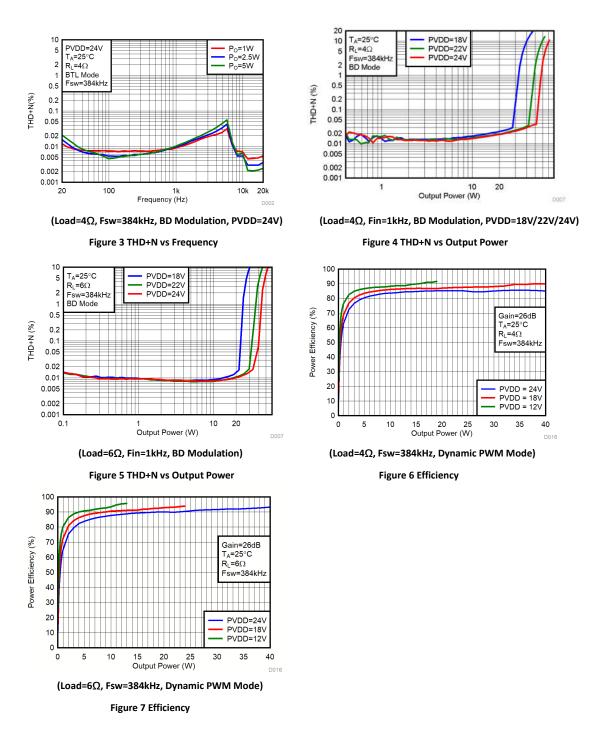

# 8.1 Bridge Tied Load (BTL) Configuration Curves with BD Mode

Free-air room temperature 25°C (unless otherwise noted.) Measurements were made using ACM3129BEVM board and Audio Precision System APX5xx Series with Analog Analyzer filter set to 20-kHz Low Pass filter. Device PWM Modulator mode set to BD mode with 384kHz Fsw, LC filter=10µH+0.68µF.

(Load= $4\Omega$ , Fsw=384kHz, BD Modulation) Figure 1 Max Output Power vs PVDD

0.02 0.01 0.005 0.002 0.001 20 100 1k Frequency (Hz)

PVDD=18V T<sub>A</sub>=25°C

R<sub>L</sub>=4Ω BTL Mode Fsw=384kH

0.5

0.1 0.05

LHD+N(%) 0.2

(Load= $4\Omega$ , Fsw=384kHz,BD Modulation, PVDD=18V)

P<sub>O</sub> =1W P<sub>O</sub> =2.5W P<sub>O</sub>=5W

20k

Figure 2 THD+N vs Frequency

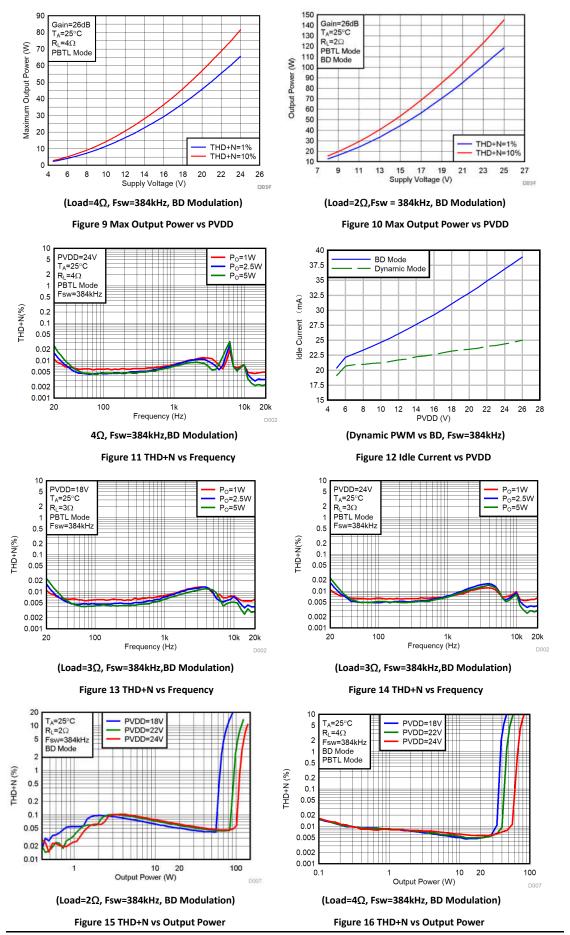

## 8.2 Parallel Bridge Tied Load (PBTL) Configuration Curves with BD Mode

Free-air room temperature 25°C (unless otherwise noted.) Measurements were made using ACM3129BEVM board and Audio Precision System APX5xx Series with Analog Analyzer filter set to 20-kHz Low Pass filter. Device PWM Modulator mode set to BD mode with 384kHz Fsw, LC filter=10µH+0.68µF.

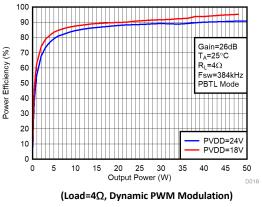

80 70 Gain=26dB Power Efficiency (%) T<sub>4</sub>=25°C 60 R<sub>L</sub>=2Ω 50 Fsw=384kHz PBTL Mode 40 30 20 PVDD=24\ PVDD=18V 20 25 30 Output Power (W) 45 50

ynamic PWM Modulation) (Load=2Ω, Dynamic PWM Modulation)

Figure 17 Efficiency vs Output Power

Figure 18 Efficiency vs Output Power

# 9. Detailed Description

## 9.1 Overview

The ACM3129B device is a highly efficient Class D audio amplifier with extreme low idle power dissipation. It can support as low as 24-mA idle loss current using standard LC filter configurations. It is integrated with 75-m $\Omega$  MOSFET that allows output currents up to 8A. The high efficiency allows the amplifier to provide an excellent audio performance without the requirement for a bulky heat sink.

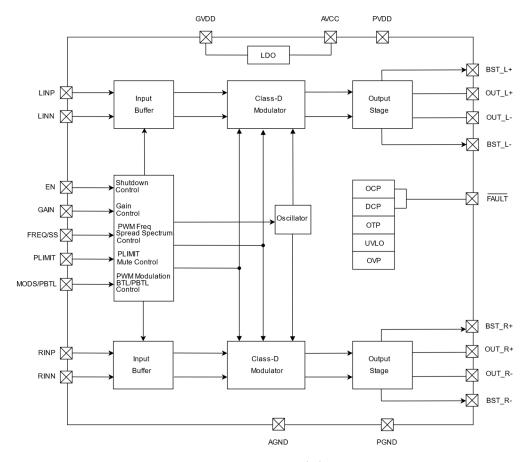

# 9.2 Functional Block Diagram

Figure 19 Function Block Diagram

# 9.3 Feature Description

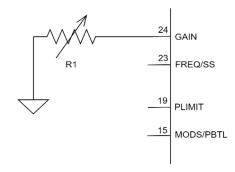

# 9.3.1 Gain Setting

The gain of the ACM3129B is set by the pull down resistor connect to GAIN control pin. The gain setting is latched during power-up and cannot be changed while device is powered. Table 1 lists the recommended resistor values and gain.

Table 1. Gain Setting

| GAIN | R1 (to GND)            | Input Impedance |

|------|------------------------|-----------------|

| 20dB | <b>47k</b> Ω           | <b>30</b> kΩ    |

| 26dB | <b>120k</b> Ω or Open  | <b>15k</b> Ω    |

| 30dB | <b>4.7k</b> Ω or Short | 9.48kΩ          |

| 34dB | 15kΩ                   | 5.987kΩ         |

Figure 20 Gain Setting

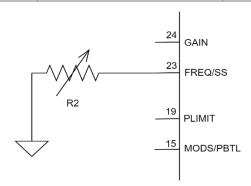

# 9.3.2 Switching Frequency Selection and Spread Spectrum Selection

The ACM3129B provides 2 switching frequency option, 384kHz and 480kHz which best balance the audio performance and power dissipation. Spread spectrum is supported by ACM3129B to minimize EMI noise.

**Table 2. Switching Frequency Selection and Spread Spectrum Setting**

| R2 (to GND)    | Switching Frequency (kHz) | Spread Spectrum |

|----------------|---------------------------|-----------------|

| 120kΩ or Open  | 384kHz                    | Disable         |

| <b>47</b> kΩ   | 480kHz                    | Disable         |

| <b>15</b> kΩ   | 480kHz                    | Enable          |

| 4.7kΩ or Short | 384kHz                    | Enable          |

Figure 21 Switching Frequency Selection and Spread Spectrum Setting

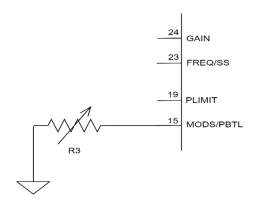

## 9.3.3 Modulation Scheme Selection and BTL/PBTL Selection

The ACM3129B provides 2 PWM Modulation Scheme, BD Modulation and Dynamic PWM Modulation. With Dynamic PWM Modulation, the amplifier's output common mode voltage keeps tracking with audio signal to minimize inductor ripple current. Compare with BD modulation, Dynamic PWM Modulation decrease power dissipation more than 40% and improve efficiency more than 5% under <1W output power.

| R3 (to GND)    | PWM Modulation Scheme | BTL/PBTL |  |  |  |

|----------------|-----------------------|----------|--|--|--|

| 120kΩ or Open  | BD                    | BTL      |  |  |  |

| 47kΩ           | BD                    | PBTL     |  |  |  |

| 15kΩ           | Dynamic PWM           | PBTL     |  |  |  |

| 4.7kO or Short | Dynamic PWM           | BTL      |  |  |  |

Table 3. Modulation Scheme Selection and BTL/PBTL Selection

Figure 22 Modulation Scheme and BTL/PBTL Selection

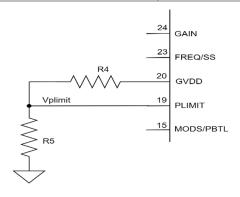

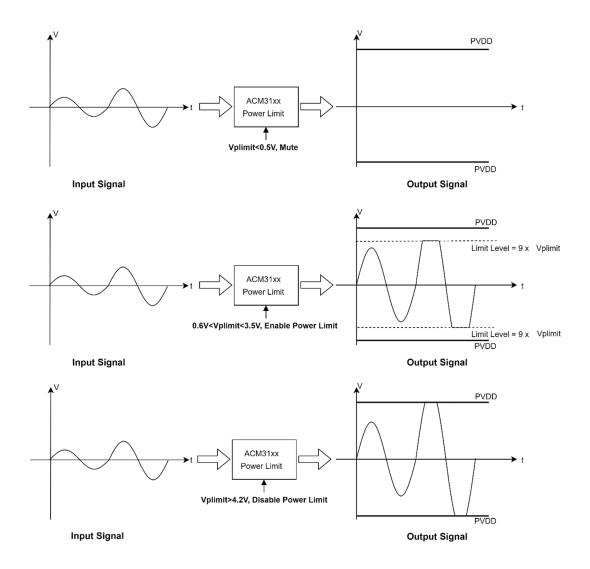

## 9.3.4 Power Limit

The voltage at PLIMIT pin can be used to limit the amplifier output.  $V_{PLIMIT}$  (at the PLIMIT pin) is set by a resistor divider from GVDD to ground.  $V_{PLIMIT}$  sets a limit on the output peak-to-peak voltage. As Figure 24 shows,  $V_{PLIMIT}$  just limit the peak-to-peak voltage but can't not been used to control the clipping depth. PLIMIT is adjustable from 0.6V to 3.5V. The output peak voltage been limited within  $^{9}\times V_{PLIMIT}$ . Set  $V_{PLIMIT}$ <0.5V, turn off output driver to mute device. Set  $V_{PLIMIT}$ >4.2V, Disable power limit function.

Table 4. Device behavior vs  $V_{\text{PLIMIT}}$

| V <sub>PLIMIT</sub> | Device behavior Description            |                                                     |

|---------------------|----------------------------------------|-----------------------------------------------------|

| <0.5V               | Mute Turn off output driver to mute de |                                                     |

| 0.6V~3.5V           | Power Limit                            | Set V <sub>PLIMIT</sub> limits output peak voltage. |

| >4.2V               | Disable Power Limit                    | Disable Power Limit                                 |

**Figure 23 Power Limit Setting**

Figure 24 Power Limit Example

## 9.3.5 Shutdown (EN) control

Pulling EN pin low will let ACM3129B operate in low-current state for power conservation. The ACM3129B outputs will enter mute once EN pin is pulled low, and regulator will also disable to save power. If let EN pin floating, the chip will enter shutdown mode because of the internal pull low resistor. For the best power-off performance, place the chip in the shutdown mode in advance of removing the power supply.

## 9.3.6 DC detection

ACM3129B has dc detection circuit to protect the speakers from large DC currents or AC current less than 2Hz which might be occurred as input capacitor defect or inputs short on printed circuit board. A DC Detect Fault is issued when the output differential voltage of either channel exceeds DC protection threshold level (2.5V Typical) for more than 700ms at the same polarity. The amplifier outputs area switched to a high impedance state when the DC Detection fault latch is engaged. The latch can be cleared by cycling the EN pin through the low state.

Connecting the FAULT and EN pins allows the FAULT pin function to automatically drive the EN pin low which clears the DC Detection protection latch.

## 9.3.7 Short-Circuit Protection and Automatic Recovery Feature

The ACM3129B has protection from over current conditions caused by a short circuit on the output stage. The short circuit protection fault is reported on the FAULT pin as a low state. The amplifier outputs are switched to a high impedance state when the short circuit protection latch is engaged. The latch can be cleared by cycling the EN pin through the low state.

If automatic recovery from the short circuit protection latch is desired, connect the FAULT pin directly to the EN pin. Connecting the FAULT and EN pins allows the FAULT pin function to automatically drive the EN pin low which clears the short-circuit protection latch.

#### 9.3.8 Thermal Protection

Thermal protection on the ACM3129B prevents damage to the device when the internal die temperature exceeds 160°C. This trip point has a +/-10°C tolerance from device to device. Once the die temperature exceeds the thermal trip point, the device enters into the shutdown state and the outputs are disabled. The over temperature protection fault is reported on the FAULT pin as a low state. The amplifier outputs are switched to a high impedance state when the over temperature protection is latched. The latch can be cleared by cycling the EN pin through the low state lasting for about 1.5S.

If automatic recovery from over temperature protection latch is desired, connect the FAULT pin directly to the EN pin. Connecting the FAULT and EN pins allows the FAULT pin function to automatically drive the EN pin low which clears the over temperature protection latch.

## 9.3.9 Over Voltage Protection

Once the PVDD votlage exceed the  $OVE_{THRES(PVDD)}$  (29.2V Typical), device will set the output driver from Play mode to Hi-Z mode. The over voltage protection fault is reported on the  $\overline{FAULT}$  pin as a low state and is latched. Once PVDD drop below 28.7V (Typical), the over voltage protection has same clear process with other DC, OC, OT protection.

## 9.3.10 Under Voltage Protection

Once the PVDD votlage drop below the  $UVE_{THRES(PVDD)}$  (4.1V Typical), device will set the output driver from Play mode to Hi-Z mode. The under voltage protection fault is reported on the FAULT pin as a low state and is latched. Once PVDD rise above 4.4V (Typical), the under voltage protection has same clear process with other DC, OC, OT protection.

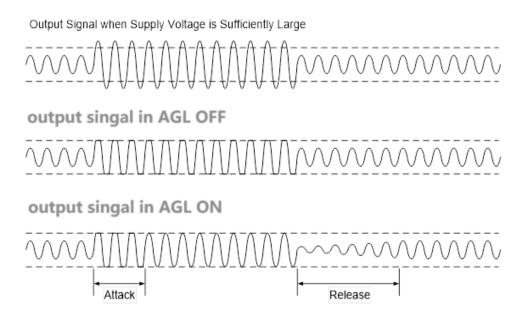

#### 9.3.11 AGL

The automatic Gain Limit is to maintain the audio outputs for a maximum voltage swing without clip distortion when excessive inputs that may otherwise cause output clippings are applied. With AGL, the ACM3129B dynamically lowers the voltage gain of both audio amplifiers to an appropriate value such that output clippings are substantially eliminated.

# 9.4 Application Information

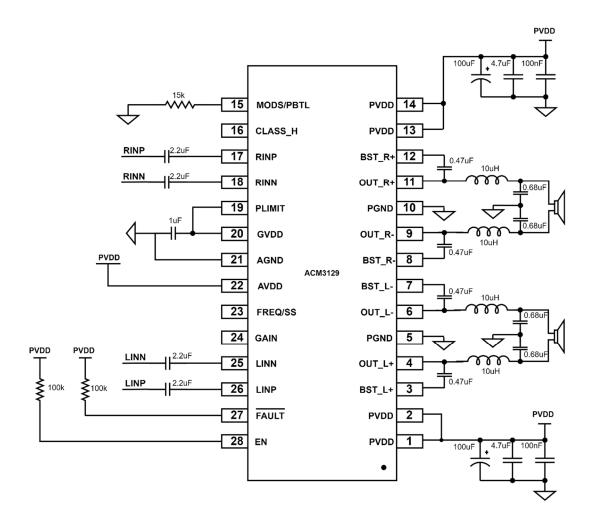

# 9.4.1 Application Circuit Example Of Stereo

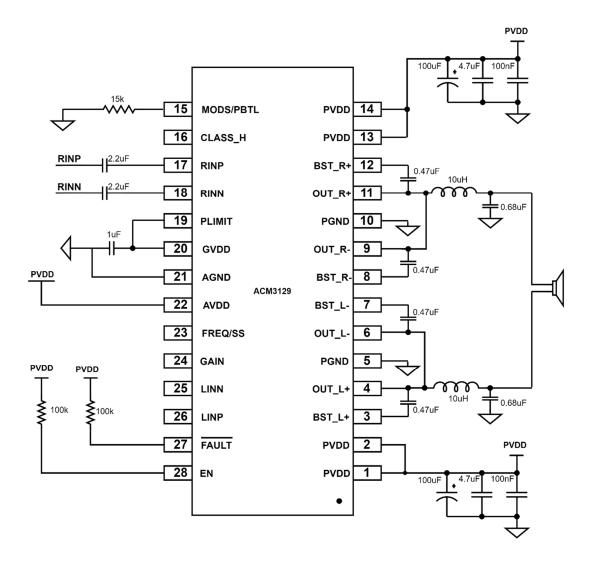

# 9.4.2 Application Circuit Example Of Mono

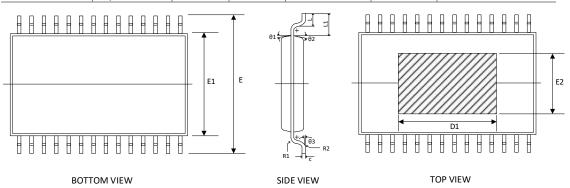

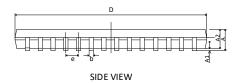

# 10. Package Dimensions

| Orderable Device | Package Type  | MPQ  | MOQ  | Eco Plan         | MSL Level | Device Marking |

|------------------|---------------|------|------|------------------|-----------|----------------|

| ACM3129B         | TSSOP28       | 3000 | 3000 | RoHS Compliant   | MSL3      | ACM3129B       |

|                  | Tape and Reel |      |      | Lead-Free Finish |           |                |

## COMMON DIMENSIONS

## (UNITS OF MEASURE=mm)

| SYMBOL | MIN  | NOM      | MAX  |

|--------|------|----------|------|

| Α      |      |          | 1.20 |

| A1     | 0.05 | 0.10     | 0.15 |

| A2     | 0.80 | 0.875    | 1.05 |

| С      | 0.09 | 0.145    | 0.2  |

| b      | 0.19 | 0.255    | 0.3  |

| L1     | 0.95 | 1.00     | 1.05 |

| L      | 0.45 | 0.6      | 0.75 |

| D1     | 5.80 | 5.90     | 6.00 |

| E2     | 2.90 | 3.00     | 3.10 |

| E      | 6.25 | 6.40     | 6.55 |

| E1     | 4.30 | 4.40     | 4.50 |

| D      | 9.60 | 9.70     | 9.80 |

| ⊝3     | 0    | 4        | 8    |

| R1     |      | 0.15 TYP |      |

| R2     |      | 0.15 TYP |      |

| Θ1     |      | 0.12 TYP |      |

| ⊝2     |      | 0.12 TYP |      |

| е      |      | 0.65mm   |      |